MC56F8025VLD

MC56F8025VLD-功能

MC56F8025VLD-数字信号控制器核心

• 具有双哈佛架构的高效 16 位 56800E 系列数字信号控制器(DSC)引擎

• 在 32MHz 核心频率下,每秒多达 3200 万次指令(MIPS)

• 单周期 16×16 位并行乘数累加器(MAC)

• 四个 36 位累加器,包括扩展位

• 32 位算术和逻辑多位移位器

• 具有独特 DSP 寻址模式的并行指令集

• 硬件 DO 和 REP 循环

• 三辆内部地址总线

• 四辆内部数据总线

• 指令集同时支持 DSP 和控制器功能

• 控制器风格的寻址模式和紧凑代码的指令

• 高效的 C 编译器和局部变量支持

• 软件子程序和中断堆栈,深度仅受内存限制

• JTAG/增强型片上仿真(OnCE),用于不显眼、与处理器速度无关的实时调试

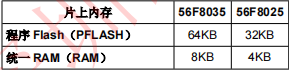

MC56F8025VLD-设备之间的差异

概述了 56F8033 和 56F8023 设备之间的关键区别

MC56F8025VLD-记忆

• 双哈佛架构允许多达三次同时访问程序和数据内存

• 防止未经授权的用户访问内部 Flash 的 Flash 安全性和保护

• 片上内存

— 64KB 的程序闪存(56F80235 设备) 32KB 程序闪存(56F8025 设备)

—8KB 的统一数据/程序 RAM(56F8035 设备) 4KB 的统一数据/程序 RAM(56F8025 设备)

• 使用 Flash 的 EEPROM 仿真功能

MC56F8025VLD-56F8035/56F8025 的外围电路

• 一个多功能六输出脉冲宽度调制器(PWM)模块

—高达 96MHz 的 PWM 工作时钟

— 15 位分辨率 —中心对齐和边缘对齐的 PWM 信号模式

—带有可编程数字滤波器的四个可编程故障输入

—双缓冲 PWM 寄存器

—每个互补的 PWM 信号对都允许从以下选择 PWM 电源源:

– PWM 发生器

– 外部 GPIO

– 内部计时器

– 模拟比较器输出

– ADC 转换结果与 ADC 高限和低限寄存器的值进行比较,以设置 PWM 输出

• 两个独立的 12 位模拟数字转换器(ADC)

— 2 x 4 通道输入

—支持同步和顺序转换

— ADC 转换可以通过 PWM 和计时器模块同步

—采样率高达 2.67MSPS

— 16 字结果缓冲寄存器

• 两个内部 12 位数字到模拟转换器(DAC)

—当输出从轨道摆动到轨道时,2 微秒的固定时间

—自动波形生成具有可编程周期、更新速率和范围的正方形、三角形和锯齿波形

• 一个 16 位多用途四定时器模块(TMR)

—高达 96MHz 的工作时钟

—八个具有级联能力的独立 16 位计数器/计时器

—每个计时器都有捕获和比较功能

—多达 12 种操作模式

• 一个具有 LIN 从属功能的队列串行通信接口(QSCI)

——全双工或单线操作

——两种接收器唤醒 方法:

– 闲置线 – 地址标记有

—四字节深的 FIFO 在发射器和接收器上都可用

• 一个排队 串行外围接口(QSPI)

—全双工操作

—主模式和从模式

—发射器和接收器上都有四字深的 FIFO

—可编程长度事务(2 至 16 位)

• 一个集成电路(I 2C)港口

— 操作量高达 400kbps

—支持主操作和从操作

—同时支持 10 位地址模式和广播模式

• 三个 16 位可编程间隔计时器(PIT)

• 两个模拟比较器(CMP)

—可选输入源包括外部引脚、DAC

—可编程输出极性

—输出可以驱动计时器输入、PWM 故障输入、PWM 源、外部引脚输出和触发 ADC

—输出下降和上升边缘检测能够产生中断 • 计算机正常运行(COP)/看门狗计时器能够选择不同的时钟源

• 多达 35 个通用 I/O(GPIO)引脚,5V 公差

• 集成开机重置(POR)和低压中断(LVI)模块• 相位锁定环路(PLL)为核心和外围设备提供高 速时钟

• 时钟来源:

—片上放松振荡器

—外部时钟:水晶振荡器、陶瓷谐振器和外部时钟源

• 用于实时调试的 JTAG/EOnCE 调试编程接

MC56F8025VLD-能源信息

• 在具有 5V 公差的高密度 CMOS 中制造

• 用于数字和模拟电路的片上调节器,以降低成本并降低噪音

• 等待和停止模式可用

• ADC 智能电源管理

• 每个外围设备都可以单独禁用以节省电力