MC9S12NE64VTUE

MC9S12NE64VTUE-简单介绍

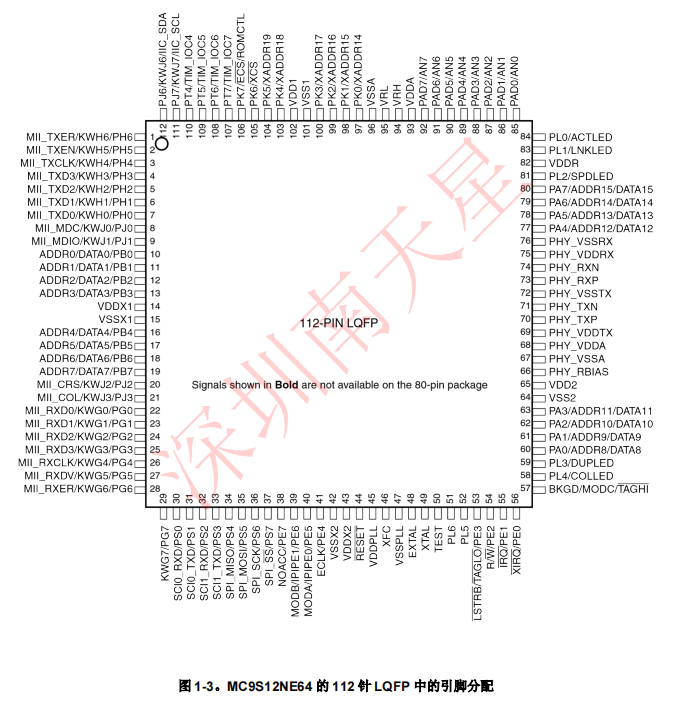

MC9S12NE64 是一个 112-/80 针具有成本效益的低端连接应用程序 MCU 系列。足够的 MC9S12NE64 由标准片上外围设备组成,包括一个 16 位中央处理器 (HCS12 CPU),64K 字节的 FLASH EEPROM,8K 字节的 RAM,集成 10/100 Mbps 以太网物理 收发器(EPHY)的以太网媒体访问控制器(EMAC),两个异步串行通信接口模块(SCI),一 个串行外围接口(SPI),一个 IC 间总线(IIC),一个 4 通道/16 位定时器模块(TIM),一个 8 通 道/10 位模拟数字转换器(ATD),最多 21 个引脚可作为键盘唤醒输入(KWU),以及两个额外 的外部异步中断。包含一个 PLL 电路允许调整功耗和性能以适应操作要求。此外,基于片上带 差距的稳压器(VREG_PHY)从3.15 V到3.45 V外部电源范围产生2.5 V(VDD)的内部数字电 源电压。足够的 MC9S12NE64 自始至终都有完整的 16 位数据路径。112 针封装版本共有 70 个 I/O 端口引脚和 10 个仅输入引脚。80 针软件包版本共有 38 个 I/O 端口引脚和 10 个仅输入引脚。

MC9S12NE64VTUE-特点

• 16 位 HCS12 核心

— HCS12 CPU

– 与 M68HC11 指令集向上兼容

– 中断堆叠和程序员模型与 M68HC11 相同

– 指令队列

– 增强的索引寻址

—内存映射和接口(MMC)

—中断控制(INT)

—后台调试模式(BDM)

—增强的 debug12 模块,包括断点和流量变化跟踪缓冲区(DBG)

—多路复用扩展总线接口(MEBI)

—仅提供 112 针软件包版本

• 唤醒中断输入

—多达 21 个端口位可用于带有数字过滤的唤醒中断功能

•记忆

— 64K 字节的 FLASH EEPROM

— 8K 字节的 RAM

• 模拟数字转换器(ATD)

—一个具有 10 位分辨率的 8 通道模块

—外部转换触发能力

• 计时器模块(TIM)

— 4 通道计时器

—每个通道可配置为输入捕获或输出比较

—简单的 PWM 模式

— 计时器计数器的模块重置

— 16 位脉冲蓄能器

—外部事件计数

— gated time accumulation

• 串行接口

—两个异步串行通信接口(SCI)

—一个同步串行外围接口(SPI)

—一辆 IC 间总线(IIC)

• 以太网媒体访问控制器(EMAC)

—符合 IEEE 802.3 标准

—中独立接口(MII)

—全双工和半双工模式

—使用暂停帧的流量控制

—MII 管理功能 —地址识别

– 带有广播地址的帧总是被接受或总是被拒绝

– 单个 48 位单独(单播)地址的完全匹配

– 组(多播)地址的哈希(64 位哈希)检查

– 滥交模式

• 以太类型过滤器

• 环回模式

• 两个接收和一个传输以太网缓冲接口

• 以太网 10/100 Mbps 收发器(EPHY)

—符合 IEEE 802.3 标准

—数字自适应均衡

—半双工和全双工

—自动协商下一页能力

—基线徘徊(BLW)校正

— 125MHz 时钟发生器和时序恢复

—集成波形电路

—环回模式

• CRG(时钟和复位发电机模块)

—有窗户的 COP 看门狗

— 实时中断

— 时钟监视器

— 皮尔斯振荡器

—锁相环时钟频率倍增器

— 在没有外部时钟的情况下,Limp 家庭模式

— 25MHz 晶体振荡器参考时钟

• 工作频率

—50 MHz 相当于单芯片的 25 MHz 总线速度

—在扩展总线模式下,32 MHz 相当于 16 MHz 的总线速度

• 内部 2.5-V 调节器

—支持 3.3 V 的输入电压范围±5%

—低功耗模式功能

—包括低压复位(LVR)电路

• 80 针 TQFP-EP 或 112 针 LQFP 封装

—多达 70 个 I/O 引脚,具有 3.3V 输入和驱动能力(112 引脚封装)

—最多两条专用的 3.3V 输入线(IRQ、XIRQ)

• 发展支持

—单线后台调试™模式(BDM)

—片上硬件断点

—增强的 DBG 调试功能

MC9S12NE64VTUE-112 针 LQFP